## 30.3 Performance Variability of a 90GHz Static CML Frequency Divider in 65nm SOI CMOS

Daihyun Lim<sup>1</sup>, Jonghae Kim<sup>2</sup>, Jean-Olivier Plouchart<sup>2</sup>, Choongyeun Cho<sup>2</sup>, Daeik Kim<sup>2</sup>, Robert Trzcinski<sup>2</sup>, Duane Boning<sup>1</sup>

<sup>1</sup>Massachusetts Institute of Technology, Cambridge, MA <sup>2</sup>IBM. Hopewell Junction. NY

A frequency divider is an essential and critical building block in high-performance clock synthesizers. Since the frequency divider operates at the highest frequency in the system in order to prescale the high-frequency VCO output, the divider speed and power trade-off should be carefully considered at an early design stage. In particular, above 50GHz, the input power reaching the frequency divider is significantly reduced by the parasitic interconnect capacitance and resistance. For limited input power, the operating range of the frequency divider is thus narrowed but must still cover the tuning range of the VCO for proper operation of the clock synthesizer. In addition to nominal speed, power and operating-range requirements, variability in the frequency divider is a critical issue for the manufacturing yield of high-speed clock synthesizers. Recently, 21.5% (3 $\sigma$ ) variation in the maximum operating frequency of dividers over a wafer in 90nm SOI technology has been reported [1]. In this paper, a static CML frequency divider is implemented in 65nm SOI CMOS technology to achieve 100GHz maximum operating frequency with 52.4mW power dissipation. Across-wafer and wafer-to-wafer variations of the divider self-oscillation frequency are measured at 80 different bias conditions using 2409 divider samples (3 divider types on each of 73 dies, for 11 wafers). The variation of critical circuit parameters for divider performance including threshold voltage, parasitic capacitance and resistance is estimated using the measurement data and sensitivity analysis at different bias conditions.

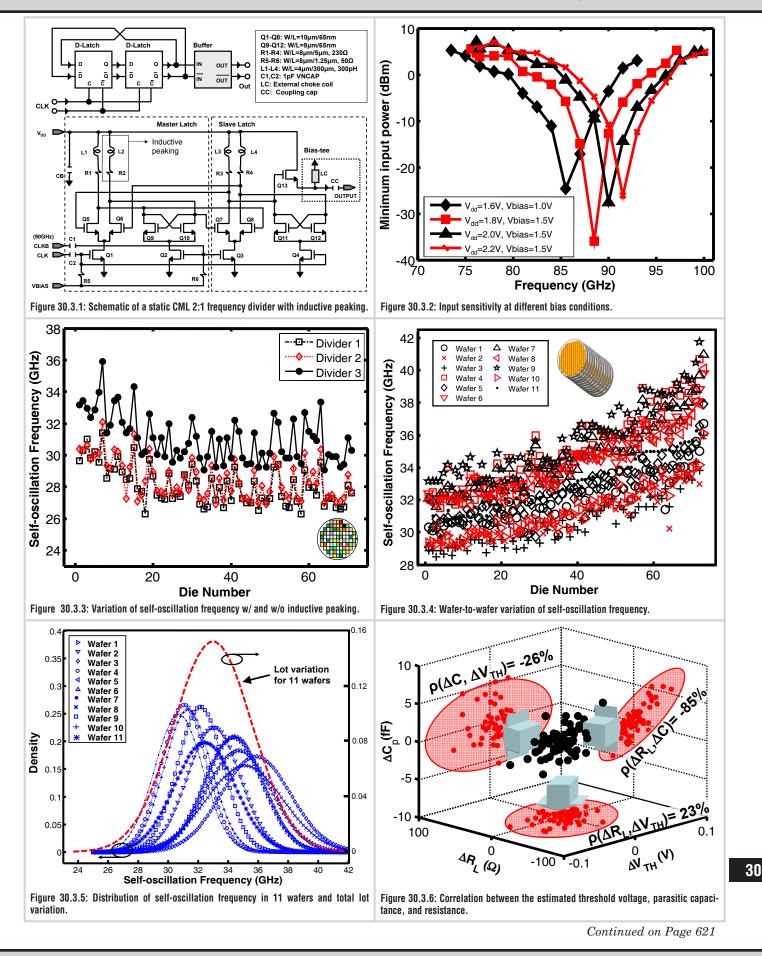

Figure 30.3.1 shows the schematic of a 2:1 static frequency divider. The divider uses CML master and slave latches with inductive peaking for bandwidth enhancement. The operating range of the frequency divider is designed to be centred at 80GHz. The bottom transistors (Q1-Q4) are sized to  $10\mu m$  to drive up to 10mA current. The size of the latch transistors (Q9-Q12) is adjusted to 8µm to reduce capacitive loading at output nodes while satisfying the selfoscillation condition  $g_{mL}R_{L}>1$  [3] with poly-silicon resistor loads. Four 300pH high-Q stab inductors are introduced to increase the bandwidth by cancelling parasitic capacitance.

Figure 30.3.2 shows the sensitivity curves of the frequency divider at 4 different bias conditions, indicating the input power required to achieve 2:1 frequency division at a given input frequency. Based on the frequency-range limitation of the equipment used in this measurement, the divider is biased to work over the input frequency range from 75 to 110GHz. The divider biased at  $2.2V V_{\text{DD}}$  and 1.5V V<sub>BIAS</sub> operates up to 100.2GHz for a 4.87dBm differential input. This is a 1.52× improvement in frequency performance over the fastest reported static frequency divider in 90nm SOI CMOS [1]. A minimum input power point is achieved at 92GHz that corresponds to a 46GHz self-oscillation frequency. The power consumption is 52.4mW and the switching energy at the self-oscillation frequency is 0.57pJ that is more than 42% reduction compared to other static frequency dividers achieving 100GHz maximum frequency in various technologies [4, 6-9]. A higher V\_DD increases the self-oscillation and maximum operating frequency, but the operating range does not change significantly. For a small input swing, the static frequency divider can be analyzed as an injection-locking oscillator, and smaller bias current (lower V<sub>BIAS</sub>) gives a wider operating range [2]. Thus, the operating range of this divider can be dynamically adjusted to the tuning range of a VCO by changing  $V_{DD}$ and V<sub>BIAS</sub>.

For functional yield and performance variation analysis, measuring the maximum operating frequency  $(F_{MAX})$  is important. However, the F<sub>MAX</sub> measurement is costly since it requires mmwave frequency sweeps and the detection of proper division. In contrast, the self-oscillation frequency is more efficient to measure and the F<sub>MAX</sub> tracks the self-oscillation frequency [1, 4]. Figure 30.3.3 shows the process variation of self-oscillation frequency when

V<sub>DD</sub>=1.8V and V<sub>BIAS</sub>=1.5V across a wafer. Divider 1 and divider 2 are identically sized, but divider 2 has more compact placement and routing for decreased wire capacitance. Divider 3 has inductive peaking in addition to the layout of divider 2. For the 3 different types of dividers, the self-oscillation frequency measurements show  $3\sigma$  of 16.7% and a 22% range between the fastest and slowest dies. In Fig. 30.3.3, divider 2 shows a 0.39GHz average improvement compared to divider 1 due to layout optimization. The inductive peaking in divider 3 results in a larger and consistent 2.57GHz average increase compared to divider 2.

While the across-wafer variation of the self-oscillation frequency is 16.7% (3 $\sigma$ ), the variation pattern across a wafer is highly systematic. Figure 30.3.4 shows the within-wafer variation for 11 different wafers at a fixed bias condition ( $V_{DD}$ =1.8V and  $V_{BIAS}$ =1.5V). Each wafer shows a similar pattern of within-wafer variation with a parallel shift: the cross correlation between different wafers is 92% on average. Based on this result, with a pre-characterized profile of a reference wafer, the performance of all dies in a random wafer can be estimated with 1.5% average error by measuring a single die and checking the difference with the reference wafer profile. Figure 30.3.5 depicts the distributions of self-oscillation frequency for each wafer based on Gaussian assumption. For the variation in waferprocessing environment, the mean value of each wafer spreads from 29.9 to 35.8GHz, and  $3\sigma$  of each wafer changes from 15% to 18%. Considering all 803 dies, 30 total variation (within-wafer and wafer-to-wafer combined) is 23.8%.

The major circuit parameters impacting the self-oscillation frequency are bias current, parasitic capacitance, and load resistance. The bias current is a strong function of the threshold voltage of input transistors. By simulation, the sensitivity of the self-oscillation frequency with respect to the change of the threshold voltage, parasitic capacitance, and load resistance can be calculated at different bias conditions. Based on a first-order performance fluctuation model, the deviation of the circuit parameters from their nominal values can be calculated using the sensitivities and the measurement data of self-oscillation frequency at 9 different bias conditions with a back-propagation of variance technique [5]. The extracted  $3\sigma$  of threshold voltage, parasitic capacitance, and resistance variation is 21%, 22% and 20%, respectively. For accurate Monte Carlo analysis of circuits using the same process, knowing the correlation between the circuit parameters is essential. The scattering plot in Fig. 30.3.6 shows a significant negative correlation ( $\rho$ =-0.85) between parasitic capacitance and resistance. The threshold voltage does not show notable correlation with other parameters. The chip micrograph of the divider circuit is shown in Fig. 30.3.7.

## Acknowledgments:

The authors thank T. Sandwick, D. Ahlgren, K. Warren, G. Patton, and L. Su at IBM for substantial contributions during various stages of this project, and A. Chandrakasan and V. Stojanovic at MIT for technical assistance.

## References:

[1] J.-O. Plouchart, J. Kim, V. Karam, et al., "Performance Variation of a 66GHz Static CML Divider in a 90nm SOI Technology," ISSCC Dig. Tech. Papers, pp. 526-527, Feb., 2006.

[2] B. Razavi, "A Study of Injection Locking and Pulling in Oscillators," IEEE J. Solid-State Circuits, vol.39, pp. 1415-1424, Sept., 2004.

[3] U. Singh, M. Green, "Dynamics of High Frequency CMOS Dividers," IEEE ISCAS, vol. 5, pp. 421-424, May, 2002.

[4] E. Laskin, S. T. Nicolson, P. Chevalier, et al., "Low-Power Low-Phase Noise SiGe HBT Static Frequency Divider Topologies up to 100GHz," IEEE Bipolar/BiCMOS Circuits and Technology Mtg, Oct., 2006.

[5] P. Drennan, C. McAndrew, "Understanding MOSFET Mismatch for Analog Design," *IEEE J. Solid State Circuits*, vol. 38, pp. 450-456, Mar., 2003

[6] D. A. Hitko, T. Hussain, J. F. Jensen, et al., "A Low Power (45mW/Latch) Static 150 GHz CML Divider," Dig. CSICS, pp. 167-170, Oct., 2004.

[7] M. Mokhtari, C. Fields, R. D. Rajavel, et al. "100+ GHz Static Divideby-2 Circuit in InP-DHBT Technology," IEEE J. Solid State Circuits, vol. 38, pp. 1540-1544, Sept., 2003.

[8] S. Trotta, H. Knapp, T. F. Meister, et al., "110-GHz Static Frequency Divider in SiGe Bipolar Technology," *Dig. CSIC*, pp. 291–294, 2005.

[9] A. Rylyakov, T. Zwick, "96-GHz Static Frequency Divider in SiGe Bipolar Technology," *IEEE J. Solid State Circuits*, vol. 39, pp. 1712–1715, Or content of the state Oct., 2004.

## **ISSCC 2007 PAPER CONTINUATIONS**

| RF OUT | GND<br>GND<br>re (20x40µm²) ar | CLKE<br>CLKE | GND<br>Stab induct | V <sub>DD</sub> |  |

|--------|--------------------------------|--------------|--------------------|-----------------|--|

|        | ge pad-sets (dir               | nension: 1.  | 3x0.5mm²)          |                 |  |

|        |                                |              |                    |                 |  |

|        |                                |              |                    |                 |  |

|        |                                |              |                    |                 |  |

|        |                                |              |                    |                 |  |

|        |                                |              |                    |                 |  |