## 25.5 A 94GHz Locking Hysteresis-Assisted and Tunable CML Static Divider in 65nm SOI CMOS

Daeik D. Kim, Jonghae Kim, Choongyeun Cho

## IBM, Hopewell Junction, NY

As an essential clock-system component, millimeter-wave dividers have been implemented for V- and W-band channels [1-8]. This has also served as a standard benchmark vehicle that reveals highspeed and low-power performances of a technology. Through technology scaling, CMOS CML static divider high-frequency performances have been scaled [6-8], and they are comparable to dividers in other technologies [1-5]. In addition to the device performance, circuit design and measurement determine the divider high-speed and wide frequency range performance. One of the uncertainties in CML static divider measurement is pulling and locking hysteresis. By using CML static divider topology, the divider has been assumed to have a fixed wide operation range, from DC to the  $f_{div,max}$ , the maximum input-referred divider operational frequency. In fact, the CML static dividers show a certain degree of locking hysteresis, similar to injection-locking dividers [9]. When the circuit sensitivity curve is measured, it is not clear where to set the threshold. Depending on the method, a sensitivity curve can be optimistic or pessimistic. A similar problem lies in the  $f_{dia,max}$ , since it changes depending on the status of a divider. Also, there have not been any analytic results that can interpret the circuit parameters and performance, in spite of the common use of sensitivity curve in literatures.

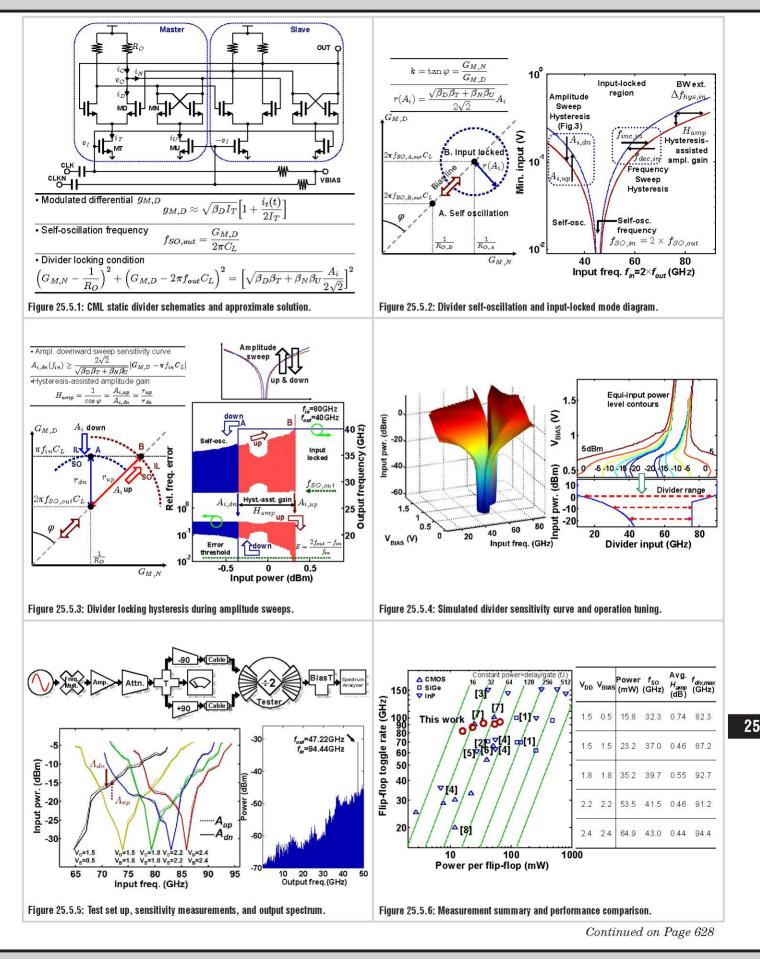

The CML static divider schematic is shown in Fig. 25.5.1. It has CML-based master-slave FF latches, with AC-coupled RF input and separate DC bias input. To maximize the divider performance, a cellbased FET layout is used with pitch relaxation. It effectively improves the device  $g_m$  by enhancing the stress liner efficiency through the opening. The FET parasitic capacitance is reduced due to the increased gate-to-contact spacing. By its nature, the divider exhibits highly nonlinear behavior. It has multiplication as a singlebalanced mixer, and the circuit behaviors are quite different in selfoscillation and input-locked modes. An approximate and linearized circuit analysis is used to obtain sensitivity curve and locking hysteresis models. The approximation begins from the tail current  $i_{T}$ modulation by input  $v_I$ , and the resulting differential-pair  $g_{MD}$ changes. By assuming that the input is much smaller than the bias tail current  $I_T$ , the modulated differential pair  $g_{MD}$  is derived with power series expansion and high-order term omission. The mixing is approximated by ignoring high-frequency terms with an assumption that they are low-pass filtered by the circuit [8]. The result will be more relevant to the high-frequency part of the divider operation due to the assumption. Another assumption is that the circuit is bistable between self-oscillation and input-locked modes. A steadystate circuit equation is established by assuming 270° phase between differential-pair input and output node  $v_0$ . In the absence of input signal  $v_L$  the self-oscillation condition and frequency are obtained. The loading capacitance is modeled as  $C_L$ . The current sum at the output node  $v_0$  is arranged in real and imaginary terms, and the Pythagorean trigonometric identity leads to a divider inputlocking condition as an equation of a circle in admittance Y plane.

The implications of the divider locking-condition equation are described in Fig. 25.5.2. Two cases - A) self-oscillation and B) inputlocked modes – are plotted on the Y=G+jB plane, where real axis is conductance G, and imaginary axis is susceptance B. The dotted line is the bias line of the differential-pair  $G_{M,D}$  and negative  $g_m$  pair  $G_{M,N}$ , and it is assumed to follow a straight line with an angle  $\varphi$ , especially when the tail device sizes are the same. First, at the self oscillation in case A, the bias point moves along the bias line, controlled by DC tail input voltage. On the other hand, for an inputlocked mode in case B, the circuit condition moves away from the bias point (the center of the circle) to a point on the circle. The radius of the circle is a function of input signal amplitude  $A_i$ . Using the input-locked and self-oscillation models, the CML static divider sensitivity curve and hysteresis effects are obtained, as given in the right plot of Fig. 25.5.2. The obtained hysteresis curves provide predicted hysteresis-assisted amplitude gain and divider operation bandwidth extension  $\Delta f_{hys,in}$ . The  $f_{in}$  is input-referred and the  $f_{out}$  is output frequency, and  $f_{in}=2 \times f_{out}$ .

The divider has hysteresis both for amplitude and frequency sweeps according to the proposed model. The amplitude sweep hysteresis model and simulations are plotted in Fig. 25.5.3. Case A is when the input signal amplitude goes down at a fixed frequency from the input-locked state. The divider remains locked until the  $r_{dn}$ , or input amplitude of  $A_{i,dn}$ . Passing  $r_{dn}$ , the divider makes a sudden transition to self-oscillation mode, since there is no solution. The downward amplitude-sweep simulation shows the consistent behavior at  $A_{i.dn}$ . Case B is when the input amplitude moves up at the same frequency from self-oscillation mode. The input modulates the divider output, and the divider tries to lock by swinging along the bias line from the center bias point, till it reaches the input frequency  $f_i$  with  $r_{up}(A_{i,up})$ . The amplitude upward-sweep simulation is consistent to this locking model. At a given bias, an analytic downward sensitivity curve is obtained as  $A_{i,dn}(f_{in})$ , by solving the minimum required amplitude for downward locking at each frequency. Using trigonometric relation, the upward sensitivity curve is  $A_{i,dn}(f_{in})/\cos\varphi$ . The hysteresis-assisted amplitude gain is  $1/\cos\varphi$ . The frequency-sweep hysteresis can be modeled similarly. There are complicated mixings well beyond the equation, but the linear model provides useful qualitative observations. The divider has AC-coupled RF input with DCbias control. Vertical native capacitors are used for AC coupling. The separate DC-bias control tunes divider operating conditions, so that the effective dividable frequency range is widely tuned as shown in Fig. 25.5.4.

The sensitivity curves of the fabricated CML static divider in 65nm SOI are measured as shown in Fig. 25.5.5. The maximum divider operational frequency is 94.446GHz with 64.9mW/FF and 86fJ power-delay product per gate at  $V_{DD}=2.4$  V and  $V_{BIAS}=2.4$  V. For each  $V_{DD}$  and  $V_{BIAS}$  setting, the upward and downward input power thresholds between self-oscillation and input-locked modes are measured. At  $V_{DD}=1.5V$  and  $V_{BIAS}=0.5V$ , the measured hysteresisassisted gain is 0.74dB. The predicted hysteresis gain is 2.55dB, with the circuit design parameter k=0.894. The minimum powerdelay product per gate of 24fJ is recorded at 82.3GHz, when  $V_{DD}$ =1.5V and  $V_{BIAS}$ =0.5V. Due to the W-band setup limitation, the lower-frequency sensitivity curve is not measured. The circuit still shows true static divider-like wide frequency range from the selfoscillation at 64.7GHz to 82.4GHz. The presented work is compared with state-of-the-art dividers in Fig. 25.5.6. The divider reaches up to 94.4GHz as a true CML static-like wide frequency range divider in CMOS, and the 24fJ power-product delay is the minimum among the dividers above 40GHz with 100×40µm<sup>2</sup> circuit area.

## Acknowledgment:

The authors acknowledge support and contributions from K. Rim, M. Kumar, C. Norris, S. Stiffler, P. Gilbert, and G. Patton from IBM SRDC, B. Floyd, J.-O. Plouchart, S. Reynolds, and R. Trzcinski at IBM T. J. Watson Research, and D. Lim from Massachusetts Institute of Technology.

## References:

E. Laskin, S. T. Nicolson, P. Chevalier, et al., "Low-Power, Low-Phase Noise SiGe HBT Static Frequency Divider Topologies Up to 100 GHz," *BCTM*, pp. 1-4, Oct. 2006.

[2] L. Wang, Y.-M. Sun, J. Borngraeber, et. al., "Low Power Frequency Dividers in SiGe:C BiCMOS Technology," SiRF Dig. Papers, pp. 357-360, Jan. 2006.

[3] D. A. Hitko, T. Hussain, D. S. Matthews, et. al., "State of the Art Low Power (42 mW per flip-flop) 150 GHz+ CML Static Divider Implemented in Scaled 0.2µm Emitter-Width InP DHBTs," Proc. InP and Related Materials Conf., pp. 85-88, May 2006.

[4] M. Sokolich, C. H. Fields, S. Thomas et. al., "A Low-Power 72.8-GHz Static Frequency Divider in AlInAs/InGaAs HBT Technology," *IEEE J. Solid-State Circuits*, vol. 36, no. 9, pp. 1328-1334, Sept. 2001.

[5] Z. Griffith, N. Parthasarathy, M. J. W. Rodwell et al. "An Ultra Low-

[5] Z. Griffith, N. Parthasarathy, M. J. W. Rodwell et al. "An Ultra Low-Power (<13.6 mW/latch) Static Frequency Divider in an InP/InGaAs DHBT Technology," *MIT-S IMS Dig.*, pp. 506-509, Jun. 2006.

Technology," MTT-S IMS Dig., pp. 506-509, Jun. 2006. [6] J.-O. Plouchart, J. Kim, V. Karam et. al., "Performance Variations of a 66GHz Static CML Divider in 90nm CMOS," ISSCC Dig. Tech. Papers, pp. 526-527, Feb. 2006.

[7] D. Lim, J. Kim, J. O. Plouchart et. al., "Performance variability of a 90GHz static CML frequency divider in 65nm SOI CMOS," *ISSCC Dig. Tech. Papers*, pp. 542-543, Feb. 2006.

[8] U. Singh and M.M. Green, "High-Frequency CML Clock Dividers in 0.13µm CMOS Operating up to 38 GHz," *IEEE J. Solid-State Circuits*, vol. 40, no. 8, pp. 1658-1661, Aug. 2005.

[9] B. Razavi, "A Study of Injection Locking and Pulling in Oscillators," IEEE J. Solid-State Circuits, vol. 39, no. 9, pp. 1415-1424, Sep. 2004.

Authorized licensed use limited to: MIT Libraries. Downloaded on October 22, 2008 at 14:03 from IEEE Xplore. Restrictions apply.

|  | Figure 25.5.7: Chip die micrograph at M10 (top) and M4 (bottom) levels. |  |

|--|-------------------------------------------------------------------------|--|

|  |                                                                         |  |

628